在模擬集成電路的設(shè)計(jì)與制造中,確保芯片的可靠性、功能完整性與長(zhǎng)期穩(wěn)定性是核心目標(biāo)。其中,靜電放電(ESD)保護(hù)電路與焊盤(PAD)電路的設(shè)計(jì),是連接芯片內(nèi)部精密模擬世界與外部物理封裝環(huán)境的關(guān)鍵橋梁,它們直接關(guān)系到芯片能否在實(shí)際應(yīng)用中抵御外部電氣沖擊并實(shí)現(xiàn)可靠的電學(xué)連接。本文將遵循典型的模擬集成電路設(shè)計(jì)流程,闡述ESD保護(hù)電路與PAD電路的設(shè)計(jì)要點(diǎn)及其在流程中的位置與作用。

一、模擬集成電路設(shè)計(jì)流程概覽

典型的模擬集成電路設(shè)計(jì)流程是一個(gè)迭代、求精的過程,主要包含以下幾個(gè)階段:

- 系統(tǒng)定義與指標(biāo)制定:明確芯片的功能、性能指標(biāo)(如增益、帶寬、噪聲、功耗等)、工作條件及封裝形式。

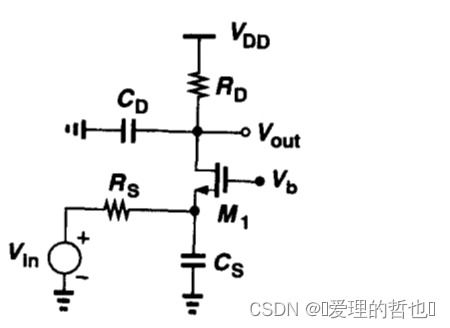

- 架構(gòu)設(shè)計(jì)與電路設(shè)計(jì):根據(jù)指標(biāo),選擇或設(shè)計(jì)合適的電路架構(gòu)(如運(yùn)算放大器、比較器、數(shù)據(jù)轉(zhuǎn)換器等),并使用晶體管級(jí)電路進(jìn)行實(shí)現(xiàn),進(jìn)行初步的仿真驗(yàn)證。

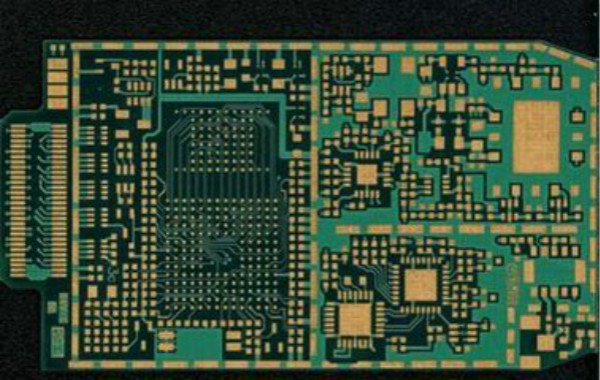

- 版圖設(shè)計(jì)與物理實(shí)現(xiàn):將電路原理圖轉(zhuǎn)化為實(shí)際的幾何圖形(版圖),這是連接電路設(shè)計(jì)與芯片制造的物理橋梁。此階段必須嚴(yán)格遵守設(shè)計(jì)規(guī)則(DRC),并考慮寄生效應(yīng)。

- 后仿真與驗(yàn)證:提取版圖的寄生參數(shù)(電阻、電容),反饋到電路仿真中,驗(yàn)證物理實(shí)現(xiàn)后的電路性能是否依然滿足指標(biāo)。同時(shí)進(jìn)行電氣規(guī)則檢查(ERC)、版圖與原理圖一致性檢查(LVS)。

- 可靠性設(shè)計(jì)與驗(yàn)證:這是ESD保護(hù)電路與PAD電路設(shè)計(jì)的核心環(huán)節(jié)。需要專門進(jìn)行ESD魯棒性設(shè)計(jì)、閂鎖效應(yīng)(Latch-up)防護(hù)設(shè)計(jì),并進(jìn)行相應(yīng)的仿真與規(guī)則檢查。

- 流片與測(cè)試:將最終確認(rèn)的版圖數(shù)據(jù)(GDSII文件)交付給晶圓廠制造,芯片返回后進(jìn)行封裝和全面的性能與可靠性測(cè)試。

ESD保護(hù)電路和PAD電路的設(shè)計(jì),主要深度融入在 “版圖設(shè)計(jì)” 與 “可靠性設(shè)計(jì)與驗(yàn)證” 階段。

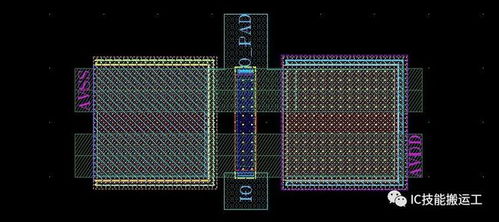

二、PAD電路:芯片與外部世界的接口

焊盤(PAD)是芯片上用于連接封裝引線或探針的金屬區(qū)域,是信號(hào)、電源和地進(jìn)出芯片的物理端口。PAD電路的設(shè)計(jì)圍繞PAD展開,其主要功能包括:

- 機(jī)械連接:提供足夠大的金屬面積,以利于引線鍵合或倒裝芯片連接,保證連接的牢固性。

- 電學(xué)連接:作為低電阻通路,將外部信號(hào)或電源引入內(nèi)部電路。

- ESD防護(hù)的錨點(diǎn):PAD通常是ESD事件(如人體放電模型HBM、機(jī)器模型MM)的首要沖擊點(diǎn),因此它是集成ESD保護(hù)結(jié)構(gòu)的核心位置。

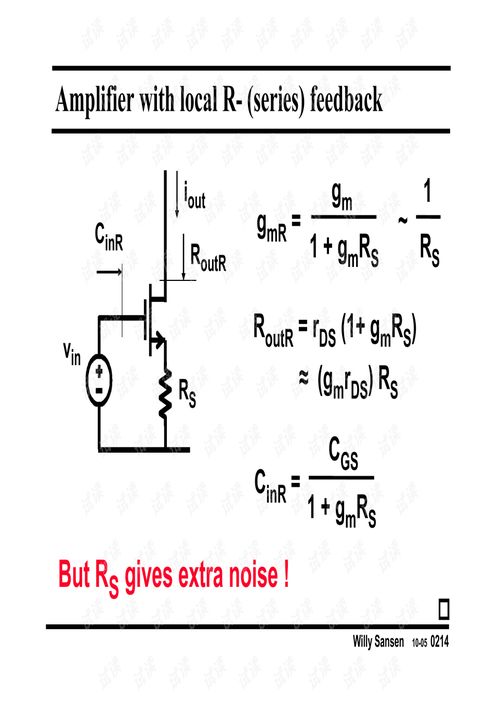

- 輸入/輸出緩沖:對(duì)于I/O PAD,內(nèi)部通常包含輸入緩沖器(將外部信號(hào)轉(zhuǎn)換為內(nèi)部邏輯電平)或輸出驅(qū)動(dòng)級(jí)(將內(nèi)部信號(hào)驅(qū)動(dòng)到外部負(fù)載)。在模擬電路中,輸入PAD可能直接連接高阻抗節(jié)點(diǎn),需特別考慮泄漏和噪聲。

PAD電路的設(shè)計(jì)需在版圖階段精心規(guī)劃,確保金屬線寬、間距滿足電流密度要求,并考慮信號(hào)完整性(如串?dāng)_)。

三、ESD保護(hù)電路:芯片的“防雷擊”系統(tǒng)

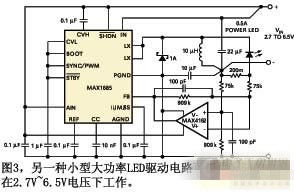

靜電放電(ESD)是集成電路在制造、封裝、測(cè)試及使用過程中面臨的主要可靠性威脅之一。ESD保護(hù)電路的作用是在ESD事件發(fā)生時(shí),在極短時(shí)間內(nèi)(納秒級(jí))為瞬態(tài)大電流提供一條安全的、低阻抗的泄放通路,將PAD上的電壓鉗位在安全范圍內(nèi),從而保護(hù)內(nèi)部脆弱的柵氧層和晶體管。

核心設(shè)計(jì)要點(diǎn)包括:

1. 保護(hù)拓?fù)浣Y(jié)構(gòu):常見的ESD保護(hù)單元包括:

* 基于二極管的結(jié)構(gòu):利用二極管的正向?qū)ê头聪驌舸┨匦孕狗烹娏鳌=Y(jié)構(gòu)簡(jiǎn)單,寄生電容小,適合高速I/O,但鉗位電壓相對(duì)固定。

- 柵極接地的NMOS(GGNMOS):最常用的結(jié)構(gòu)之一。在ESD事件下,其寄生雙極型晶體管(NPN)被觸發(fā)導(dǎo)通,形成低阻通路。其觸發(fā)電壓和維持電壓是關(guān)鍵設(shè)計(jì)參數(shù)。

- 可控硅整流器(SCR):?jiǎn)挝幻娣e泄放電流能力最強(qiáng),但觸發(fā)電壓可能較高,且存在閂鎖風(fēng)險(xiǎn),需謹(jǐn)慎使用。

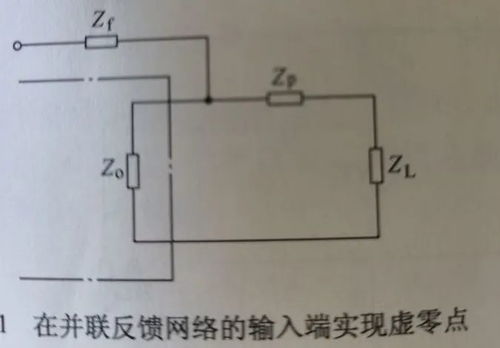

- 兩級(jí)保護(hù)策略:為了兼顧響應(yīng)速度與泄放能力,常采用兩級(jí)保護(hù)。

- 第一級(jí)(主保護(hù)):位于PAD附近,通常采用大尺寸器件,用于泄放絕大部分ESD電流,承受主要能量沖擊。

- 第二級(jí)(次級(jí)保護(hù)):位于內(nèi)部電路輸入端附近,尺寸較小,用于鉗制第一級(jí)保護(hù)后可能殘留的過沖電壓,提供精細(xì)保護(hù)。兩級(jí)之間通常用串聯(lián)電阻隔離。

- 全芯片ESD保護(hù)網(wǎng)絡(luò):不僅要保護(hù)每個(gè)I/O PAD,還需設(shè)計(jì)電源軌(VDD到VSS)之間的保護(hù)電路(如電源鉗位電路),確保任何組合引腳之間(如I/O到VDD, I/O到VSS, VDD到VSS)都有有效的ESD泄放路徑。

- 版圖實(shí)現(xiàn):ESD器件的版圖設(shè)計(jì)有特殊規(guī)則,例如采用“叉指”結(jié)構(gòu)增加周長(zhǎng)、添加足夠的接觸孔、確保電流均勻分布、遵守安全的間距規(guī)則以防止二次擊穿等。

四、設(shè)計(jì)流程中的協(xié)同與驗(yàn)證

在完整的模擬IC設(shè)計(jì)流程中,ESD/PAD設(shè)計(jì)并非孤立環(huán)節(jié):

- 在電路設(shè)計(jì)階段,就需要預(yù)估PAD和ESD結(jié)構(gòu)引入的寄生電容(尤其是對(duì)高速、高頻模擬信號(hào)的影響),并將其納入整體性能仿真。

- 在版圖設(shè)計(jì)階段,必須根據(jù)晶圓廠提供的ESD設(shè)計(jì)規(guī)則(ESD Rule Deck)進(jìn)行布局布線。PAD的位置規(guī)劃、ESD保護(hù)環(huán)(Guard Ring)的繪制、電源/地網(wǎng)絡(luò)的布局都至關(guān)重要。

- 在驗(yàn)證階段,除了常規(guī)的DRC/LVS,必須執(zhí)行專門的ESD規(guī)則檢查(ESD Check),確保所有保護(hù)結(jié)構(gòu)符合規(guī)范,泄放路徑完整且低阻。還可能進(jìn)行傳輸線脈沖(TLP)特性的電路級(jí)仿真,以預(yù)測(cè)ESD器件的觸發(fā)特性。

結(jié)論

ESD保護(hù)電路與PAD電路是模擬集成電路從設(shè)計(jì)圖紙走向可靠產(chǎn)品的關(guān)鍵保障。它們的設(shè)計(jì)緊密集成于芯片的物理實(shí)現(xiàn)與可靠性驗(yàn)證流程之中。優(yōu)秀的ESD/PAD設(shè)計(jì)需要在保護(hù)能力、信號(hào)完整性、面積開銷和工藝兼容性之間取得精妙平衡。隨著工藝節(jié)點(diǎn)不斷演進(jìn),內(nèi)部晶體管柵氧層日益脆弱,而封裝形式愈發(fā)多樣,這對(duì)ESD保護(hù)與接口電路的設(shè)計(jì)提出了更高要求,使其成為模擬及混合信號(hào)IC設(shè)計(jì)中不可或缺的專業(yè)領(lǐng)域。